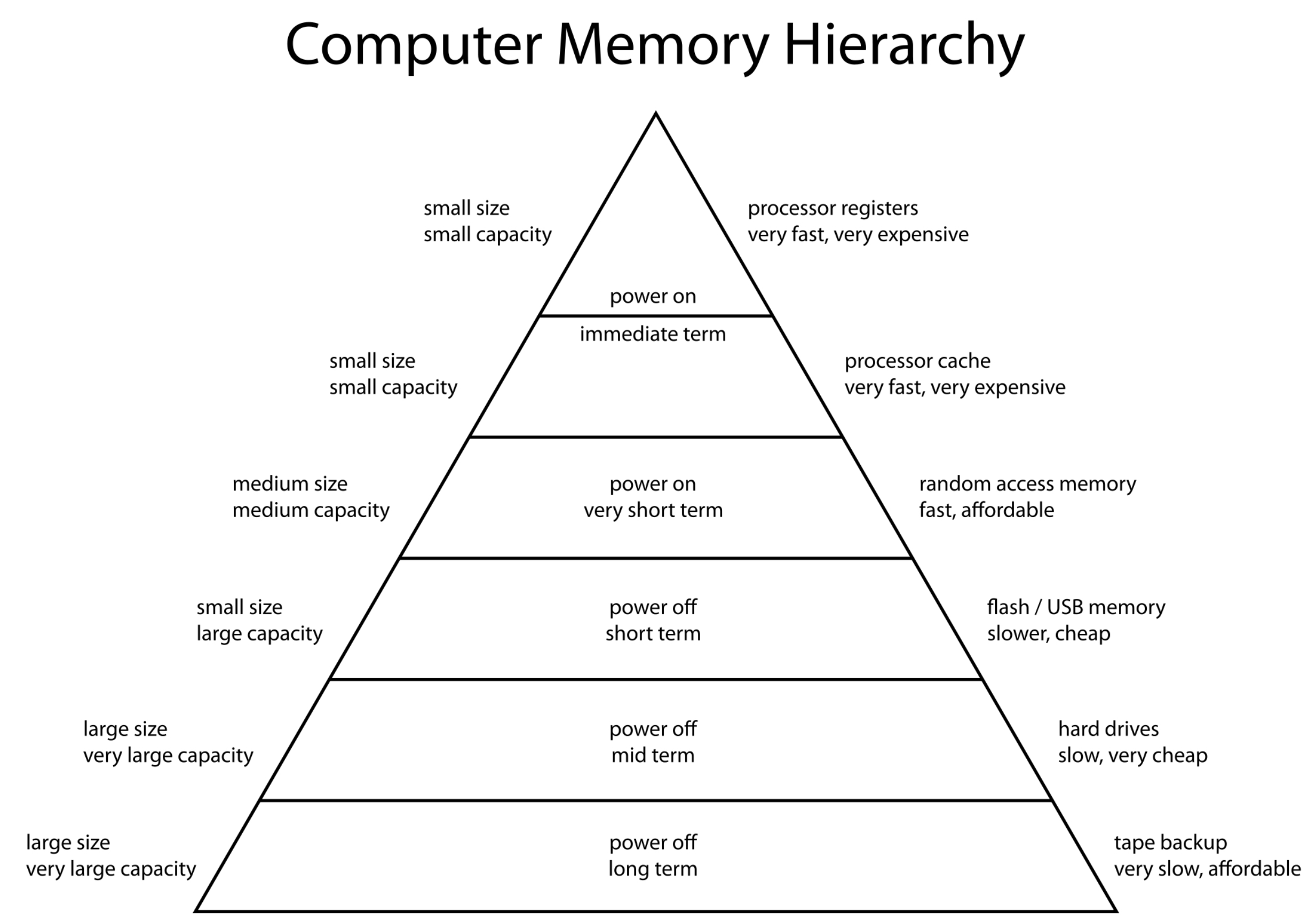

The quest for a “universal memory” is the search for a new memory technology that replaces all or part of the standard memory hierarchy in computers today—from processor registers, to on-chip static-random-access memory (SRAM) to cascades of one, two, three, and even four caches to external dynamic RAM (DRAM) to flash (electrically erasable nonvolatile RAM) as caches to hard disks, and ultimately to tape archives.

Most new memory technologies today are not aimed at becoming universal memories, but to merely replace one of the members of the hierarchy with a better technology, as exemplified by high-end laptops now using only solid-state flash chips instead of bulky mechanical hard disks, and using the cloud for backup rather than tape drives.

The quest for “universal memory” is aimed at ultimately replacing the entire memory hierarchy with a single technology, albeit a layer at a time (in the manner in which advanced driver-assistance capabilities, such as collision avoidance, lane-changing warnings, and automatic parking in cars are slowly evolving toward the completely driverless car).

is being challenged by “universal memory” types that are as fast as registers but as dense as tape.

Source: Public Domain

For instance, Japan’s SpriteSat, which observes atmospheric anomalies, chose to use Everspin’s nonvolatile magnetic random access memory (MRAM, which permanently stores data even if the power goes down) instead of standard static RAM (SRAM, which is fast but volatile) backed-up by a level of flash memory (which is slower, but nonvolatile). In particular, SpriteSat uses MRAM with its sensors to serve as the controlling microprocessor’s “universal memory.”

Finding a truly universal memory technology may take decades, but solid progress is being made. For nearly two years, IBM (which invented spin-transfer torque memory) and Samsung (which has flexible memory foundries) have been collaborating on the development of a Spin-Transfer Torque (STT) MRAM that uses individual electrons to represent 1s and 0s, instead of the thousands of electrons needed to switch a traditional MRAM cell’s magnetic orientation to represent 1s and 0s. The resulting STT MRAMs could elevate memory applications from sensor-controllers like SpriteSat’s to the larger market of mobile and Internet of Things (IoT) devices.

Said Daniel Worledge, Distinguished Research Staff Member and senior manager of MRAM at IBM Research, “While no truly universal memory for high-performance applications is likely to be developed any time soon, the killer app for spin-torque MRAM is as a ‘universal memory’ for mobile and IoT applications that value ultra-low power, non-volatility, high density, and unlimited endurance over breakneck speed (5 to 10 nanosecond read/write cycle times).”

Although no one questions that a single universal memory type capable of handling all applications would be ideal, some experts point out the advantages of hierarchical tiers of memory types, despite their excessive power consumption and programming complexity. Says Gary Grider, leader of the High Performance Computing division at Los Alamos National Laboratory in New Mexico, “Crushing too many tiers of storage into too few levels is as bad as having too many levels. APIs [application programmer interfaces] are different for different tiers of data storage/memory to highlight the many orders of magnitude differences in bandwidth and latency, as well as access methods that are cumbersome or impossible with different storage devices or media.”

The head of the Moscow Institute of Physics and Technology (MIPT) Laboratory of Functional Materials and Devices for Nanoelectronics, Andrey Zenkevich, is hopeful about the potential for a solution using the insulator hafnium oxide. MIPT’s memory technology has been proven in the lab to be faster than static random-access memory (SRAM), has a lower power requirement than combined metal oxide semiconductors (CMOS), and is non-volatile like flash, hard drives, and tape storage. Zenkevich concedes, however, that development efforts underway for many years still fall short of commercialization.

“Ever since hafnium dioxide was integrated with CMOS technology as a high-k gate dielectric to replace silicon dioxide (around 2007), there have been significant research efforts to use it as a functional material in a fast, low-power, non-volatile memory device ultimately aiming at the development of universal memory,” Zenkevich said.

The non-profit consortium SemaTech‘s research labs have tried to use hafnium dioxide as a storage medium by using conductive filaments to change its resistance. These resistive RAMs (ReRAMS) have also been researched using titanium (instead of hafnium) dioxide by Hewlett Packard in cooperation with Korean memory giant Hynix; after eight years of development efforts, the technology is still not ready for commercialization.

While such wonder materials are in development, universal memory is being approximated by a new breed of “virtual” memories using software/hardware solutions that abstract a memory location by offering indirect addressing to data wherever it resides. Such interim solutions make invisible to the programmer the intricacies of addressing, managing, and securing the different types of memory devices in the hierarchy. However, critics say the reason hierarchical memories were developed in the first place was to increase the performance of algorithms by allowing the programmer to take advantage of the different trade-offs of memories at different levels in the hierarchy.

“Memory hierarchies that are invisible to the programmer are great for inexperienced programmers, but not so good for sophisticated programmers. ‘Invisible to the programmer’ is wasteful of a machine’s capabilities, even though it may be more efficient for the programmer,” said Grider. “Wasteful of a machine is typical when saving programmer time, but undesirable if you are trying to solve problems that require more computer power than you have, or are able to buy, or to pay the cost of supplying them enough power. In that case, you have to give the programmer access to memory tier controls in order to make tradeoffs that get the most out of the computer.”

Another contender as a true universal memory developed by Texas Instruments (TI), among others, is called ferroelectric random access memory (FeRAM). Since 2011, TI has made available small microcontrollers that use FeRAMs to eliminate the need for a memory hierarchy, for applications such as in-the-field data loggers that sense and archive various sensor measurements like temperature, humidity, vibration, pressure, motion, and pollutants. By increasing the speed of FeRAMs to rival SRAM and shrinking them down to the size of DRAMs, but still offering the low power requirement and non-volatility of flash, TI and others are readying a new generation of FeRAMs that could act as universal memories for high-performance applications.

IBM Zurich also has developed a phase-change memory (PCM) technology that could collapse the same four levels (SRAM, DRAM, flash, and hard disks) as FeRAM. Even though it has been prototyped, the company is playing down its imminent commercialization. “PCM does hold the promise of become a type of universal memory, if its speed and density can be boosted by further research, but IBM is not depending on it,” said Jeff Barber, vice president of high-end storage at IBM America.

Barber’s words reflect the broken promises of earlier purported universal memory “breakthroughs,” such as the failure of resistive RAM. Also, North Carolina State University’s double floating-gate field-effect-transistor (FET), heralded in 2011 as a potential universal memory breakthrough, has so far failed commercialization efforts, according to its inventors.

Other options are on the horizon, but no one knows whether they can be commercialized. Cornell University, for instance, claims to have to created a magnetoelectric memory technology that uses 10 times less energy than IBM/Samsung’s STT-MRAM. Based on a “multiferroic” material that joins the magnetic properties of MRAM with the ferroelectric properties of FRAM, the technology saves energy by switching from 1 to 0, or visa versa, via a voltage potential field alone—with no current flowing.

Likewise magnetoelectric multiferroics, magnetoelectric multipoles, and ferroelastics have each been shown in the lab to exhibit various properties of ferromagnetics and ferroelectrics, but have yet to prove their ability to be manufactured in production quantities.

Will the venerable memory hierarchy continue to reign supreme despite the worldwide efforts to achieve the “dream” of a universal memory? Only time will tell.

IBM, for instance, is pouring millions of dollars into commercializing various memory technologies, but is also making yearly advances in faster, denser memory storage technologies. Also, users of tape memories are actually growing in number, because of the technology’s ability to achieve what is called a zero-loss recovery point objective (RPO) by doing complete memory image backups as often as 10 times a day in as little as three seconds to installations as much as 1,000 miles away.

Besides RPO, however, much data is accessed so infrequently that it is suitable for online tape archives. The use of tape virtualization software and the allure of RPO are keeping the bottom tier of the memory hierarchy secure for the foreseeable future.

IBM’s Barber says that, aside from paper printouts, tape is the only memory technology immune to the electromagnetic pulse of a nuclear explosion, so “the storage hierarchy is here to stay.”

R. Colin Johnson is a Kyoto Prize Fellow who has worked as a technology journalist for two decades.

Join the Discussion (0)

Become a Member or Sign In to Post a Comment